# Optimizing Setup Conditions for High Accuracy Measurements of the HI5741

Application Note May 1996 AN9619

#### Introduction

The HI5741 is a 14-bit 100MHz Digital to Analog Converter. This current out DAC is designed for low glitch and high Spurious Free Dynamic Range operation. As a result of its inherently high dynamic range, special care must be taken to assure that any accuracy measurements made on the device are not corrupted by external stimuli introduced by the measurement equipment being used. The purpose of this application note is to outline proven measurement techniques (both static and dynamic) to assure accurate Digital to analog converter performance is observed.

# Measuring Spurious Free Dynamic Range (SFDR)

The Spurious Free Dynamic Range of the HI5741 DAC is the most important specification for communication applications. This specification shows how Integral Linearity, Glitch, and Switching Noise affect the spectral purity of the output signal. Several important things must be noted first.

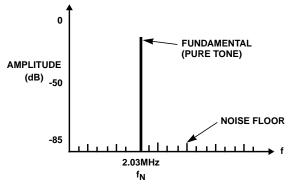

When a quantized signal is reconstructed, certain artifacts are created. Let's take the example of trying to recreate a 2.03MHz sine wave with a  $1\mbox{V}_{\mbox{P-P}}$  output. In the frequency domain the fundamental should appear at 2.03MHz as shown in Figure 1.

FIGURE 1. SIGNAL CHARACTERISTICS

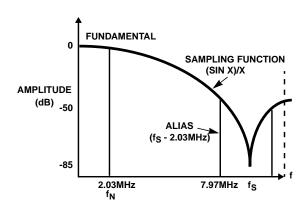

The fundamental of a pure 2.03MHz tone should appear as an impulse in the frequency domain at 2.03MHz. In a sampled system noise terms are produced near the sampling frequencies called aliases. These aliases are related to the fundamental in that they are located at  $\pm f_N$  around the sampling frequency as shown in Figure 2.

So for a 2.03MHz fundamental and a 10MHz sampling rate an alias term is created at 7.97MHz and 12.03MHz. A (SIN (X))/X function shaping is also induced by sampling a signal. Aliases continue up through the frequency spectrum repeating around the sampling frequency and its harmonics (i.e.,  $2f_S$ ,  $3f_S$ ,  $4f_S$ ).

FIGURE 2. ALIASING CHARACTERISTICS OF SAMPLED SYSTEMS

Since the highest spur (either harmonically or nonharmonically related) with respect to the fundamental will define the dynamic range of the system, it is used to define the Spurious Free Dynamic Range of the converter.

#### **Checking Your Setup**

Measuring the spectral performance of high speed DACs with high degrees of dynamic range presents an interesting problem during the course of device or system evaluation. In the case of the HI5741 in particular, the device in many cases exhibits levels of dynamic range that either equal or exceed those of the measurement device used.

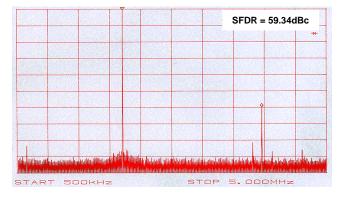

The problem arises in that the noise floor performance observed when using a spectrum analyzer to measure the DAC varies depending on the settings for resolution bandwidth (RBW) and mixer attenuation which are used. By adjusting these two settings, one can artificially make the spectral performance of the DAC look worse than it really is. This phenomena can be attributed to a variety of factors, the most dominant of which is the sensitivity of the analyzer itself. As a general rule, adjusting the mixer (or internal) attenuation on a spectrum analyzer should not result in any change in measured harmonic performance. A change in the harmonic power of the signal is a good indicator of a possible saturation condition on the mixer, which needs to be corrected prior to making final measurements. Increasing the mixer attenuation does have some drawbacks, however, namely an increase in noise floor power, which needs to be compensated for by decreasing the resolution bandwidth. This issue can be seen by observing the spectral sweeps shown in Figures 3 and 4. In both cases, a 2.03MHz fundamental was created at a clock rate of 10MHz. In addition, 16dB of external attenuation was used in all cases.

Figure 3 illustrates the output of the spectrum analyzer (in this case an HP8560E) as seen with no mixer attenuation using a resolution bandwidth of 100Hz. The first thing that one notices by observing this figure is that the second harmonic distortion is much higher than one would expect for a 14-bit converter (59.5dB below the fundamental).

FIGURE 3. SPECTRAL PERFORMANCE WITH NO INTERNAL ATTENUATION

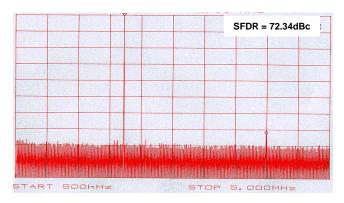

FIGURE 4. SPECTRAL PERFORMANCE WITH 20dB INTERNAL ATTENUATION

In Figure 4, one can see the vast improvement in spectral purity obtained by simply adding 20dB of internal attenuation to the mixer. Note dynamic range over the entire band of interest. Also of note is the increased noise floor characteristic of the spectrum (approximately 15dB average increase) over then entire band. As stated earlier, this is expected when introducing internal attenuation.

The use of external attenuation can also play a significant role in dynamic range measurements. As a rule of thumb, adjusting the external attenuation of the signal (not to be confused with the mixer or internal attenuation) should result in a dB-for-dB drop in both carrier and harmonic power. If an increase in external attenuation results in an increase in measured dynamic range, the previous measurement was once again limited by the analyzer.

All this being said, the fundamental problem still exists in that one must still make dynamic range measurements in excess of 80dBc over a relatively large frequency span, a condition which most modern spectrum analyzers cannot readily accommodate. As a result, the use of signal filtering needs to play an important role in the course of evaluating performance.

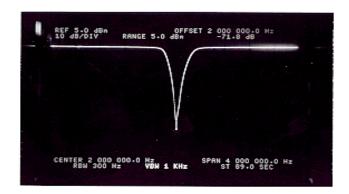

The use of filtering can dramatically ease the problems described above with respect to measuring dynamic range. By using a good quality notch filter, one can eliminate the need to adjust mixer attenuation and in turn bring to bear the full dynamic range of the spectrum analyzer. Figure 5 illustrates the characteristics of such a notch filter.

FIGURE 5. NOTCH FILTER CHARACTERISTICS

The three fundamental characteristics which make the use of a notch filter desirable for this type of testing are:

- a) Attenuation of the Fundamental. By attenuating the fundamental, which is the spur with by far the most power in the spectrum, one dramatically decreases the burden on the spectrum analyzer to accurately measure the performance of the device under test.

- b) **Quick Recovery**. By making the attenuation band as narrow as possible, the filter again allows the evaluator to get an accurate depiction of the device's performance without having to worry about attenuation of any harmonic distortion generated by the converter.

- c) Low Insertion Loss. While insertion loss in and of itself can be dealt with when making measurements, lower insertion loss makes the job of characterizing the HI5741 less cumbersome.

As one can see from Figure 5, the filter used to make the described measurements possesses a >60dB notch with a 100kHz attenuation band and negligible insertion loss.

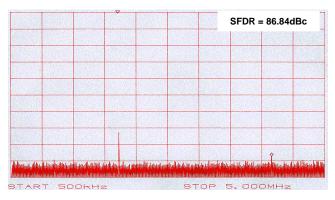

As stated earlier, the introduction of a notch filter to the system allows the evaluator to bring the full dynamic range of the spectrum analyzer to bear when making measurements. As seen in Figure 6, this can result in a significant improvement in the measured dynamic range of the HI5741.

While these high quality filters can be quite expensive and cumbersome to use at times, the goal of filter use is to ascertain the actual device or system level performance, not enhance it.

FIGURE 6. SPECTRAL PERFORMANCE OF THE HI5741

### Linearity

Linearity measurements on Digital-to-Analog converters are typically performed in a static state. An input code is generated and presented to the digital inputs of the converter. The converter is then strobed (or clocked) to pass the data through the converter. After a predetermined amount of wait time has passed (to assure the output of the DAC has settled), the output of the converter is then measured several times (to eliminate the presence of noise) and an average output voltage is recorded. Once all of the data has been collected, an LSB (or Least Significant Bit) size is computed based on the following equation:

$$LSB = \frac{(FSR)}{2^{n} - 1}$$

(EQ. 1)

Where FSR is defined as the full scale range of the converter and *n* is the resolution (number of bits).

Once the LSB size has been computed for the converter being tested, the linearity performance (both Integral and Differential) can be computed by the following equations:

$$INL = \frac{(V_{CODE} - ((LSB \bullet CODE) + OFFSET))}{LSB}$$

(EQ. 2)

$$DNL = \left(\frac{(V_{CODE} - V_{CODE - 1})}{LSB}\right) - 1$$

(EQ. 3)

Where  $V_{CODE}$  is the voltage measured on the load resistor at a given code,  $V_{CODE-1}$  is the voltage measured on the load resistor at the previous code and OFFSET is the offset voltage of the converter (or voltage output at CODE = 0).

While the same fundamental concepts of measuring linearity apply to high resolution converters as for lower (10 bits and below) resolution DACs, special care must be taken to avoid thermal effects from degrading performance. Unlike dynamic testing, where the voltage created on a load resistor is changing very rapidly, the nature of linearity testing allows the thermal characteristics of these resistors to come into play.

Typical temperature coefficient ratings for such resistors are quoted to be in the 100ppm to 200ppm per degree Celsius

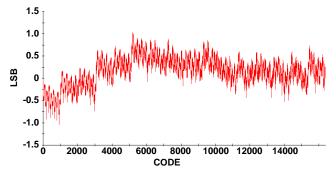

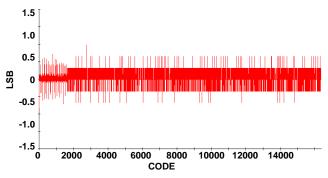

range. In the case of the HI5741, which has an LSB size of approximately  $60\mu V$ , this TC performance can result in as much of 3 LSB of error in linearity. To avoid this, the use of low temperature coefficient resistors ( $40ppm/^{O}C$  maximum) will effectively remove the effects of thermal drift from linearity measurements of the HI5741. Refer to Figures 7 and 8 below for the typical linearity performance of the HI5741 using the methods outlined above.

FIGURE 7. TYPICAL HI5741 INL

FIGURE 8. TYPICAL HI5741 DNL

## **Board Layout Considerations**

A task that can be just as challenging, if not more frustrating as making sure the measurement equipment being used reports both repeatable and realistic numbers, is the that of making sure that the evaluation platform (specifically the PCB) does not introduce unwanted noise.

Series Termination Resistors - As with any mixed signal design, it is important to keep noise generated from high speed digital signals from corrupting high accuracy analog data. To assist with this effort, the use of series termination resistors, which interact with the input capacitance of the device, provide an adequate low pass filter. The choice of resistor value depends on the requirements set by the system being designed. The only restriction when choosing a resistor value is that of voltage drop across the resistor, which will be driven by the input current of the device. The worst case specification for input current on the HI5741 is 700µA, which needs to be taken into consideration to make sure enough amplitude remains to trigger the device.

The frequency response of the low pass filter can be determined by the following equation:

$$f_{\text{CUTOFF}} = \frac{1}{2\pi RC}$$

(EQ. 4)

Where R is the series resistor being solved for, and C is the input capacitance of the HI5741. Since the input capacitance of the device will vary depending on lot to lot variation through manufacturing, one should use the worst case capacitance value of 5pF (as opposed to the typical 3pF stated in data sheets) in determining the appropriate cutoff frequency.

In addition to series termination resistors, trace lengths on the digital inputs should be kept as short and closely matched as possible. At high frequencies, large mismatches in trace lengths on the data lines can generate excessive noise and in extreme cases can result in a setup time violation on the DAC.

**Output Loading** - Care should be taken to assure that the loads on the two analog outputs of the DAC ( $I_{OUT}$  and  $I_{OUTB}$ ) are as closely matched as possible. Trace lengths should be closely matched and high precision resistors should be used to assure any impedance mismatch is minimized as seen inside the device.

**Power Planes** - Careful consideration must be taken when laying out the power planes of high speed devices as well. In the case of the HI5741, this consists of three power planes (V<sub>CC</sub>, V<sub>FF</sub> and GND).

Since the only device connection to  $V_{CC}$  is strictly digital in nature, the  $V_{CC}$  plane can be one solid sheet as long as it is appropriately decoupled to the digital ground plane.

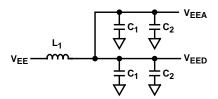

In the case of  $V_{EE}$ , particular care should be taken since this is the substrate potential of the HI5741. In order to avoid a loop which will create additional noise at the device, the  $V_{EE}$  supply should be brought in at one central location, and distributed to the  $V_{EE}$  plane through a ferrite bead connection (to reject high frequency noise) to the device as seen in Figure 9 below.

FIGURE 9. RECOMMENDED SUPPLY CONNECTION

In addition, supply decoupling should be placed as close to each pin as possible.

Separate ground planes should be provided and tied together at one central, low impedance ( $<10\Omega$ ) location.

#### **Conclusion**

As had been outlined in this document, the task of making realistic accuracy measurements on a 14-bit Digital to Analog converter such as the HI5741 can be a demanding task. By using the procedures described, the evaluator will be able to obtain a true picture of the actual performance of the device or system being evaluated. Using filtering, low drift resistors and following the board layout guidelines presented, make it possible to achieve dynamic range measurements in excess of 80dB.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com